# ANALOG MONITORING AND CONTROL CIRCUIT

# FEATURES

- 12-Bit ADC (200kSPS):

- Eight Analog Inputs

- Input Range 0 to 2 × V<sub>REF</sub>

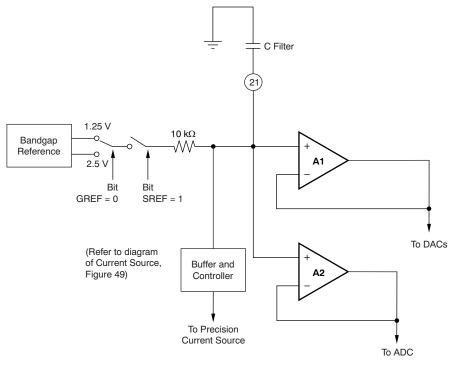

- Programmable V<sub>REF</sub>, 1.25V or 2.5V

- Eight 12-Bit DACs (2µs Settling Time)

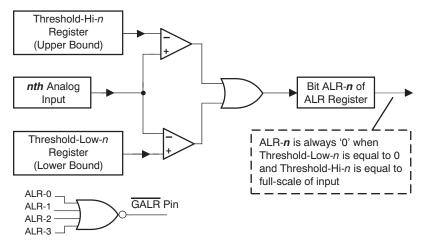

- Four Analog Input Out-of-Range Alarms

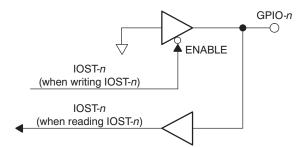

- Six General-Purpose Digital I/O

- Internal Bandgap Reference

- **On-Chip Temperature Sensor**

- **Precision Current Source**

- SPI<sup>™</sup> Interface, 3V or 5V Logic Compatible

- Single 3V to 5V Supply

- Power-Down Mode/Low Power

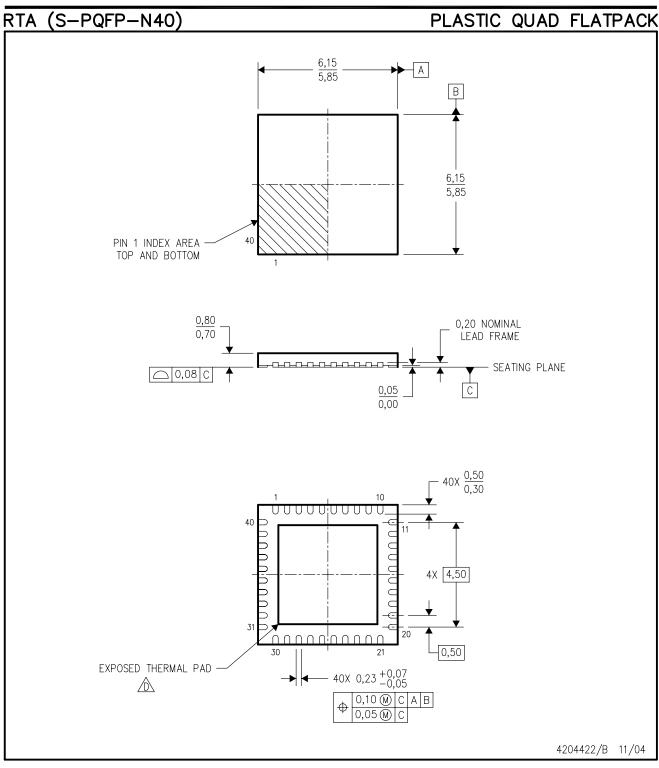

- Small Package (QFN-40, 6 x 6 mm)

# APPLICATIONS

- **Communications Equipment** •

- **Optical Networks**

- **Automatic Test Equipment**

- **Industrial Control and Monitor** .

- **Medical Equipment**

# DESCRIPTION

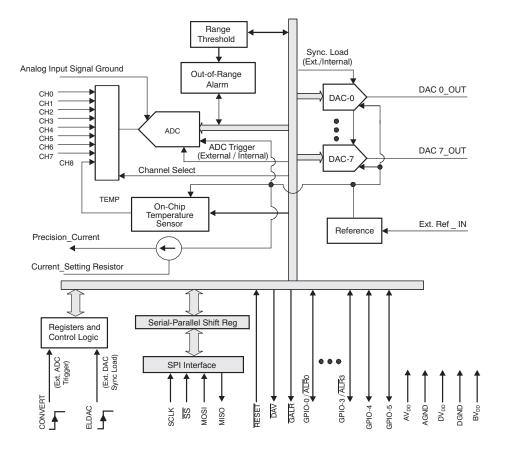

The AMC7823 is a complete analog monitoring and control circuit that includes an 8-channel, 12-bit analog-to-digital converter (ADC), eight 12-bit digitalto-analog converters (DACs), four analog input out-of-range alarms, and six GPIOs to monitor analog signals and control external devices. Also, the AMC7823 has an internal sensor to monitor chip temperature, and a precision current source to drive remote thermistors, or RTDs, to monitor remote temperatures.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SPI is a trademark of Motorola, Inc.

All other trademarks are the property of their respective owners.

# **DESCRIPTION (CONTINUED)**

The AMC7823 has an internal programmable reference (+2.5V or +1.25V), and an SPI serial interface. An external reference can be used as well. Typical power dissipation is 100mW. The analog input range is 0V to +5V, and the analog output range is 0V to +2.5V or 0V to +5V. The AMC7823 is ideal for multichannel applications where low power and small size are critical. The AMC7823 is available in a 40-lead QFN package and is fully specified over the  $-40^{\circ}$ C to +85°C temperature range.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

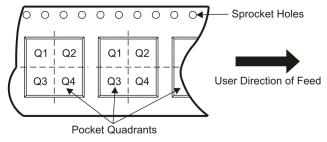

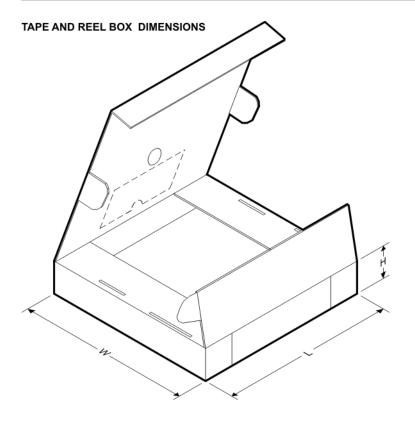

#### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT  | PACKAGE-<br>LEAD<br>(DESIGNATOR) | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|----------|----------------------------------|-----------------------------------|--------------------|--------------------|------------------------------|

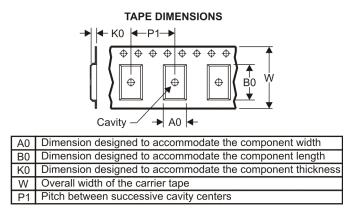

| AMC 7922 |                                  | -40C to +85C                      | AMC7823            | AMC7823IRTAT       | Tape and Reel, 250           |

| AIMC7023 | MC7823 QFN-40 (RTA)              | -400 10 +650                      | AMC7823            | AMC7823IRTAR       | Tape and Reel, 2000          |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                                                               | PARAMETER         | AMC7823                         | UNIT |

|---------------------------------------------------------------|-------------------|---------------------------------|------|

| AV <sub>DD</sub> , DV <sub>DD</sub> , BV <sub>DD</sub> to GND |                   | -0.3 to +6                      | V    |

| Digital input voltage to GND                                  |                   | -0.3 to BV <sub>DD</sub> + 0.3  | V    |

| Analog input voltage to GND                                   |                   | -0.3 to AV <sub>DD</sub> + 0.3  | V    |

| Input current, continuous                                     |                   | ±20                             | mA   |

| Input current, momentary                                      |                   | ±100                            | mA   |

| Operating temperature range                                   |                   | -40 to +105                     | °C   |

| Storage temperature range                                     |                   | -65 to +150                     | °C   |

| Junction temperature range (T <sub>J</sub> r                  | nax)              | +150                            | °C   |

| Power dissipation                                             |                   | $(T_J max - T_A) / \theta_{JA}$ | W    |

| Thermalimnedance                                              | θ <sub>JC</sub>   | 15                              | °C/W |

| Thermal impedance                                             | θ <sub>JA</sub>   | 60                              | °C/W |

| Lood tomporature (coldering)                                  | Vapor phase (60s) | +215                            | °C   |

| Lead temperature (soldering)                                  | Infrared (15s)    | +220                            | °C   |

(1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

SLAS453D-APRIL 2005-REVISED AUGUST 2008

# **ELECTRICAL CHARACTERISTICS: +5V**

At -40°C to +85°C,  $AV_{DD} = 5V$ ,  $DV_{DD} = 5V$ ,  $BV_{DD} = 3V$  to 5V, using external 2.5V reference, unless otherwise noted.

| PARAMETER                                   | TEST CONDITIONS                                                                                       | MIN   | TYP   | MAX                | UNIT               |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|--------------------|--------------------|

| ADC ANALOG INPUTS                           |                                                                                                       |       |       |                    |                    |

| Input voltage range                         |                                                                                                       | 0     |       | $2 \times V_{REF}$ | V                  |

| Input impedance                             |                                                                                                       |       | 5     |                    | MΩ                 |

| Input capacitance                           |                                                                                                       |       | 15    |                    | pF                 |

| Input leakage current                       |                                                                                                       |       | ±1    |                    | μA                 |

| ANALOG-TO-DIGITAL CONVERTER                 |                                                                                                       |       |       |                    |                    |

| Resolution                                  |                                                                                                       |       |       | 12                 | Bits               |

| No missing codes                            |                                                                                                       | 12    |       |                    | Bits               |

| Integral linearity                          |                                                                                                       | -1.25 |       | +1.25              | LSB <sup>(1)</sup> |

| Differential linearity                      |                                                                                                       | -1    |       | +1.25              | LSB                |

| Offset error                                |                                                                                                       |       |       | ±2                 | LSB                |

| Offset error drift                          |                                                                                                       |       | ±4    |                    | ppmFS/°C           |

| Offset error match                          |                                                                                                       |       | 0.5   | 1                  | LSB                |

| Gain error                                  |                                                                                                       |       |       | ±6                 | LSB                |

| Gain error match                            |                                                                                                       |       | 0.3   | 1                  | LSB                |

| Noise                                       |                                                                                                       |       | 70    |                    | $\mu V_{RMS}$      |

| Power-supply rejection                      | $AV_{DD} = 5V \pm 5\%$                                                                                |       | 70    |                    | dB                 |

| Sample rate <sup>(2)</sup>                  |                                                                                                       |       | 200   |                    | kHz                |

| Total conversion time                       | Scan Channels 0 through 7                                                                             |       | 45    |                    | μs                 |

| Total conversion time including temperature | Scan Channels 0 through 8                                                                             |       | 56    |                    | μs                 |

| Channel-to-channel isolation                | $V_{IN} = 5V_{PP}$ at 10kHz                                                                           |       | 0.5   |                    | LSB                |

| DIGITAL-TO-ANALOG CONVERTER <sup>(3)</sup>  |                                                                                                       |       |       |                    |                    |

| Output voltage range                        | Programmable                                                                                          | 0     |       | $2 \times V_{REF}$ | V                  |

| Output current                              | Refer to Typical Characteristics                                                                      |       | ±1    |                    | mA                 |

| Resolution                                  |                                                                                                       |       |       | 12                 | Bits               |

| Integral linearity <sup>(4)</sup>           |                                                                                                       |       | ±2    | ±8                 | LSB                |

| Monotonicity                                |                                                                                                       | 12    |       |                    | Bits               |

| Differential linearity                      |                                                                                                       |       | ±0.2  | ±1                 | LSB                |

| Offset error                                | Output range = 0 to V <sub>REF</sub>                                                                  |       | ±0.5  | ±5                 | mV                 |

| Onset end                                   | Output range = 0 to $2 \times V_{REF}$                                                                |       | ±1    | ±10                | mV                 |

| Offset error drift                          |                                                                                                       |       | ±4    |                    | ppmFS/°C           |

| Gain error                                  | Output range = 0 to 2 × V <sub>REF</sub>                                                              |       | ±0.3  | ±1.0               | %FS                |

| Settling time                               | Step between code 0x400 to 0xC00, to ±1LSB                                                            |       | 2     |                    | μs                 |

| Code change glitch                          | 1LSB change, in worst case                                                                            |       | 20    |                    | nV-s               |

| Overshoot                                   | Step between code 0x400 to 0xC00                                                                      |       | 200   |                    | mV                 |

| Crosstalk                                   | Step between code 0x400 to 0xC00                                                                      |       | < 0.5 |                    | LSB                |

| Signal-to-noise ratio                       | Sine wave (1kHz, $5V_{PP}$ ) generated by DAC, sampling at 400kSPS, $R_L = 10k\Omega$ , $C_L = 100pF$ |       | 74    |                    | dB                 |

|                                             | Output buffer gain = 2                                                                                |       | 60    |                    | nV/√Hz             |

| Output noise voltage density                | Output buffer gain = 1                                                                                |       | 30    |                    | nV/√Hz             |

(1) LSB means least significant bit.

(2) Single-channel conversion only. Does not include control logic delay associated with ADC operation, such as from the trigger signal to the start of conversion.

(3) DAC is tested with load of  $25k\Omega$  in parallel with 100pF to ground.

(4) Measured from code 0x008 to 0xFFF.

#### www.ti.com

# ELECTRICAL CHARACTERISTICS: +5V (continued)

At -40°C to +85°C,  $AV_{DD}$  = 5V,  $DV_{DD}$  = 5V,  $BV_{DD}$  = 3V to 5V, using external 2.5V reference, unless otherwise noted.

|                                                                 |                                     |       | AMC7823 | 3                      |        |

|-----------------------------------------------------------------|-------------------------------------|-------|---------|------------------------|--------|

| PARAMETER                                                       | TEST CONDITIONS                     | MIN   | TYP     | MAX                    | UNIT   |

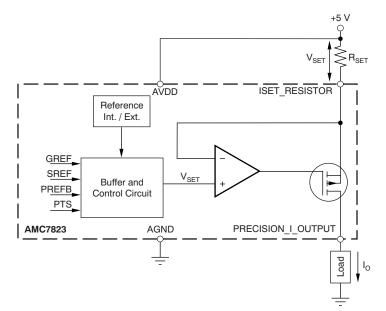

| PRECISION CURRENT SOURCE                                        |                                     | ł     |         |                        |        |

| Output current range                                            |                                     | 0.01  |         | 10                     | mA     |

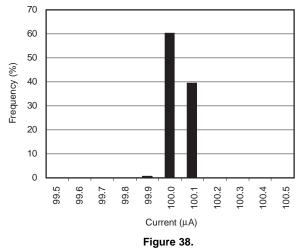

| Output current accuracy                                         | I <sub>out</sub> = 100μA            | 99.5  | 100.0   | 100.5                  | μA     |

| Output current drift                                            | I <sub>out</sub> = 100μA            |       | 40      |                        | ppm/°C |

| Output impedance                                                | I <sub>out</sub> = 100μA            |       | 100     |                        | MΩ     |

| Compliance voltage of pin<br>PRECISION_I_OUTPUT                 | I <sub>out</sub> = 10mA             | 3     | 4.25    |                        | V      |

| Power-supply rejection ratio                                    |                                     |       | 60      |                        | dB     |

| VOLTAGE REFERENCE (V <sub>REF</sub> )                           |                                     | ł     |         |                        |        |

| Internal reference voltage <sup>(5)</sup>                       | At +25°C                            | 2.495 | 2.50    | 2.505                  | V      |

| Internal reference drift                                        | -40C to +85°C                       |       | ±15     |                        | ppm/C  |

| Output impedance of pin EXT_REF_IN as internal reference output |                                     |       | 10      |                        | kΩ     |

| Short-circuit current                                           |                                     |       | 250     |                        | μA     |

| External reference voltage                                      |                                     | 1.20  |         | 2.55                   | V      |

|                                                                 | Internal reference selected         |       | 10      |                        | kΩ     |

| External reference input resistance                             | Internal reference de-selected      |       | 1       |                        | MΩ     |

| External reference input capacitance                            |                                     |       | 5       |                        | pF     |

| TEMPERATURE SENSOR                                              |                                     | I     |         |                        |        |

| Temperature range                                               |                                     | -40   |         | +85                    | °C     |

| Deschutter                                                      | V <sub>REF</sub> = 2.5V             |       | +3.2    |                        | °C     |

| Resolution                                                      | V <sub>REF</sub> = 1.25V            |       | +1.6    |                        | °C     |

| A                                                               | V <sub>REF</sub> = 2.5V             |       | ±4      |                        | °C     |

| Accuracy                                                        | V <sub>REF</sub> = 1.25V            |       | ±2.0    |                        | °C     |

| LEVEL OF PIN GALR AND DAV                                       |                                     | ł     |         |                        |        |

| I <sub>OH</sub> = 0.7mA                                         |                                     | 4     |         | $DV_{DD}$              | V      |

| I <sub>OL</sub> = 180μA                                         |                                     | 0     |         | 0.4                    | V      |

| DIGITAL INPUT/OUTPUT, EXCEPT PIN                                | GALR AND DAV                        |       |         |                        |        |

| V <sub>IH</sub>                                                 | $BV_{DD} = 5V, I_{IH} = 5\mu A$     | 3.5   |         | BV <sub>DD</sub> + 0.3 | V      |

| V <sub>IL</sub>                                                 | $BV_{DD} = 5V, I_{IL} = -5\mu A$    | 0     |         | 0.8                    | V      |

| V <sub>OH</sub> Logic level                                     | $BV_{DD} = 5V, I_{OH} = -3mA$       | 4     |         | BV <sub>DD</sub>       | V      |

| V <sub>OL</sub>                                                 | $BV_{DD} = 5V, OL = 3mA$            | 0     |         | 0.4                    | V      |

| V <sub>IH</sub>                                                 | $BV_{DD} = 3V$ , $I_{IH} = 5\mu A$  | 2.1   |         | BV <sub>DD</sub> + 0.3 | V      |

| Vii                                                             | $BV_{DD} = 3V$ , $I_{IL} = -5\mu A$ | 0     |         | 0.6                    | V      |

| V <sub>OH</sub> Logic level                                     | $BV_{DD} = 3V$ , $I_{OH} = -3mA$    | 2.4   |         | BV <sub>DD</sub>       | V      |

| V <sub>IL</sub>                                                 | $BV_{DD} = 3V, I_{OL} = 3mA$        | 0     |         | 0.4                    | V      |

| Input capacitance                                               |                                     |       | 5       |                        | pF     |

(5) Bit GREF in AMC Status/Configuration Register determines the internal reference voltage. The internal  $V_{REF} = 2.5V$  when GREF = 1, and the internal  $V_{REF} = 1.25V$  when GREF = 0 (see AMC Status/Configuration Register for details).

#### www.ti.com

# ELECTRICAL CHARACTERISTICS: +5V (continued)

At -40°C to +85°C,  $AV_{DD}$  = 5V,  $DV_{DD}$  = 5V,  $BV_{DD}$  = 3V to 5V, using external 2.5V reference, unless otherwise noted.

|                                       |                                 |                                                                   | A    | MC7823 |      |      |  |

|---------------------------------------|---------------------------------|-------------------------------------------------------------------|------|--------|------|------|--|

| PARAMETER                             |                                 | TEST CONDITIONS                                                   | MIN  | ТҮР    | MAX  | UNIT |  |

| POWER-                                | SUPPLY REQUIREMENTS             | I                                                                 |      |        |      |      |  |

| Power-                                | AV <sub>DD</sub>                |                                                                   | 2.7  | 5      | 5.5  | V    |  |

| supply                                | DV <sub>DD</sub> <sup>(6)</sup> |                                                                   | 2.7  |        | 5.5  | V    |  |

| voltage                               | BV <sub>DD</sub> <sup>(7)</sup> |                                                                   | 2.7  |        | 5.5  | V    |  |

| Quiescent current of AV <sub>DD</sub> |                                 | In normal operation,<br>precision current source = 0, no DAC load | 15 2 |        | 20   | mA   |  |

|                                       | 20                              | All power-down                                                    |      | 1      |      |      |  |

| Quiescen                              | t current of DV <sub>DD</sub>   |                                                                   |      | 0.3    |      | mA   |  |

| Quiescen                              | t current of BV <sub>DD</sub>   |                                                                   |      | 0.1    |      | mA   |  |

| Power dis                             | ssipation                       |                                                                   |      | 100    |      | mW   |  |

| TEMPER                                | ATURE RANGE                     | · · · ·                                                           |      |        |      |      |  |

| Specified                             | performance                     |                                                                   | -40  |        | +85  | С    |  |

| Storage                               |                                 |                                                                   | -65  |        | +150 | С    |  |

$\begin{array}{ll} \mbox{(6)} & \mbox{DV}_{DD} \mbox{ must equal } AV_{DD}. \\ \mbox{(7)} & \mbox{BV}_{DD} \mbox{ must not be greater than } AV_{DD} \mbox{ or } DV_{DD}. \end{array}$

www.ti.com

# **ELECTRICAL CHARACTERISTICS: +3V**

At -40°C to +85°C, AV<sub>DD</sub>, DV<sub>DD</sub>, BV<sub>DD</sub> = 3V, using external 1.25V reference, unless otherwise noted.

|                                             |                                                                                                             |       | AMC7823 |                    |                    |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|---------|--------------------|--------------------|

| PARAMETER                                   | TEST CONDITIONS                                                                                             | MIN   | ТҮР     | MAX                | UNIT               |

| ADC ANALOG INPUTS                           |                                                                                                             |       |         |                    |                    |

| Input voltage range                         |                                                                                                             | 0     |         | $2 \times V_{REF}$ | V                  |

| Input impedance                             |                                                                                                             |       | 5       |                    | MΩ                 |

| Input capacitance                           |                                                                                                             |       | 15      |                    | pF                 |

| Input leakage current                       |                                                                                                             |       | ±1      |                    | μA                 |

| ANALOG-TO-DIGITAL CONVERTER                 |                                                                                                             |       |         |                    |                    |

| Resolution                                  |                                                                                                             |       |         | 12                 | Bits               |

| No missing codes                            |                                                                                                             | 12    |         |                    | Bits               |

| Integral linearity                          |                                                                                                             | -1.25 |         | +1.25              | LSB <sup>(1)</sup> |

| Differential linearity                      |                                                                                                             | -1    |         | +1.25              | LSB                |

| Offset error                                |                                                                                                             |       |         | ±3                 | LSB                |

| Offset error drift                          |                                                                                                             |       | ±4      |                    | ppmFS/°C           |

| Offset error match                          |                                                                                                             |       | 0.5     | 1                  | LSB                |

| Gain error                                  |                                                                                                             |       |         | ±12                | LSB                |

| Gain error match                            |                                                                                                             |       | 0.3     | 1.5                | LSB                |

| Noise                                       |                                                                                                             |       | 70      |                    | μV <sub>RMS</sub>  |

| Power-supply rejection                      | $AV_{DD} = 3V \pm 5\%$                                                                                      |       | 70      |                    | dB                 |

| Sample rate <sup>(2)</sup>                  |                                                                                                             |       | 200     |                    | kHz                |

| Total conversion time                       | Scan Channels 0 through 7                                                                                   |       | 47      |                    | μs                 |

| Total conversion time including temperature | Scan Channels 0 through 8                                                                                   |       | 58      |                    | μs                 |

| Channel-to-channel isolation                | $V_{IN} = 2.5V_{PP}$ at 10kHz                                                                               |       | 0.5     |                    | LSB                |

| DIGITAL-TO-ANALOG CONVERTER <sup>(3)</sup>  |                                                                                                             |       | I       |                    |                    |

| Output voltage range                        | Programmable                                                                                                | 0     |         | $2 \times V_{REF}$ | V                  |

| Output current                              | Refer to Typical Characteristics                                                                            |       | ±1      |                    | mA                 |

| Resolution                                  |                                                                                                             |       |         | 12                 | Bits               |

| Integral linearity <sup>(4)</sup>           |                                                                                                             |       | ±2      | ±8                 | LSB                |

| Monotonicity                                |                                                                                                             | 12    |         |                    | Bits               |

| Differential linearity                      |                                                                                                             |       | ±0.2    | ±1                 | LSB                |

|                                             | Output range = 0 to V <sub>REF</sub>                                                                        |       | ±0.5    | ±5                 | mV                 |

| Offset error                                | Output range = 0 to 2 x V <sub>REF</sub>                                                                    |       | ±1      | ±10                | mV                 |

| Offset error drift                          |                                                                                                             |       | ±4      |                    | ppmFS/°C           |

| Gain error                                  | Output range = 0 to 2 x V <sub>REF</sub>                                                                    |       | ±0.2    | ±1.0               | %FS                |

| Settling time                               | Step between code 0x400 to 0xC00,<br>to ±1LSB                                                               |       | 2       |                    | μs                 |

| Code change glitch                          | 1LSB change, in worst case                                                                                  |       | 20      |                    | nV-s               |

| Overshoot                                   | Step between code 0x400 to 0xC00                                                                            |       | 200     |                    | mV                 |

| Crosstalk                                   | Step between code 0x400 to 0xC00                                                                            |       | <0.5    |                    | LSB                |

| Signal-to-noise ratio                       | Sine wave (1kHz, $5V_{PP}$ ) generated by DAC,<br>sampling at 400kSPS, $R_L = 10k\Omega$ ,<br>$C_L = 100pF$ |       | 74      |                    | dB                 |

|                                             | Output buffer gain = 2                                                                                      |       | 60      |                    | nV/√Hz             |

| Output noise voltage density                | Output buffer gain = 1                                                                                      |       | 30      |                    | nV/√Hz             |

(1) LSB means least significant bit.

(2) Single-channel conversion only. Does not include control logic delay associated with ADC operation, such as from the trigger signal to the start of conversion.

(3) DAC is tested with load of  $25k\Omega$  in parallel with 100pF to ground.

(4) Measured from code 0x008 to 0xFFF.

#### www.ti.com

# ELECTRICAL CHARACTERISTICS: +3V (continued)

At -40°C to +85°C,  $AV_{DD}$ ,  $DV_{DD}$ ,  $BV_{DD}$  = 3V, using external 1.25V reference, unless otherwise noted.

|                   |                                                   |                                  | AMC7823<br>MIN TYP M/ |       | 5                      |        |

|-------------------|---------------------------------------------------|----------------------------------|-----------------------|-------|------------------------|--------|

|                   | PARAMETER                                         | TEST CONDITIONS                  | MIN                   | TYP   | MAX                    | UNIT   |

| PRECISI           | ON CURRENT SOURCE                                 |                                  |                       |       |                        |        |

| Output cu         | urrent range                                      |                                  | 0.01                  |       | 10                     | mA     |

| Output cu         | urrent accuracy                                   | $I_{out} = 100 \mu A$            | 99.5                  | 100.0 | 100.5                  | μA     |

| Output cu         | urrent drift                                      | $I_{out} = 100 \mu A$            |                       | 40    |                        | ppm/°0 |

| Output im         | npedance                                          | $I_{out} = 100 \mu A$            |                       | 100   |                        | MΩ     |

|                   | ice voltage of pin<br>ON_I_OUTPUT                 | $AV_{DD} = 2.7V, I_{out} = 10mA$ | 1.9                   | 2     |                        | V      |

| Power-su          | pply rejection ratio                              |                                  |                       | 60    |                        | dB     |

| VOLTAG            | E REFERENCE (V <sub>REF</sub> )                   |                                  |                       |       |                        |        |

| Internal re       | eference voltage <sup>(5)</sup>                   | At +25°C                         | 1.247                 | 1.25  | 1.253                  | V      |

| Internal re       | eference drift                                    | –40C to +85°C                    |                       | ±20   |                        | ppm/°0 |

|                   | npedance of pin EXT_REF_IN<br>al reference output |                                  |                       | 10    |                        | kΩ     |

| Short-circ        | cuit current                                      |                                  |                       | 125   |                        | μΑ     |

| External r        | reference voltage                                 |                                  | 1.20                  |       | 1.28                   | V      |

| External r        | reference input resistance                        |                                  |                       | 10    |                        | kΩ     |

| External r        | reference input capacitance                       |                                  |                       | 5     |                        | pF     |

| TEMPER            | ATURE SENSOR                                      | _                                |                       |       |                        |        |

| Temperature range |                                                   |                                  | -40                   |       | 85                     | °C     |

| Resolution        |                                                   |                                  |                       | 1.6   |                        | °C     |

| Accuracy          | ,                                                 |                                  |                       | ±2.0  |                        | °C     |

| LEVEL O           | F PIN GALR AND DAV                                | · ·                              |                       |       | <u>.</u>               |        |

|                   | I <sub>OH</sub> = 0.3mA                           |                                  | 2.4                   |       | $DV_{DD}$              | V      |

|                   | I <sub>OL</sub> = 125μΑ                           |                                  | 0                     |       | 0.4                    | V      |

| DIGITAL           | INPUT/OUTPUT, EXCEPT PIN                          | GALR AND DAV                     | H                     | 1     |                        |        |

| VIH               |                                                   | I <sub>IH</sub> = 5μA            | 2.1                   |       | BV <sub>DD</sub> + 0.3 | V      |

| V <sub>IL</sub>   | -                                                 | $I_{IL} = -5\mu A$               | 0                     |       | 0.6                    | V      |

| V <sub>OH</sub>   | – Logic level                                     | $I_{OH} = -3mA$                  | 2.4                   |       | $BV_{DD}$              | V      |

| V <sub>OL</sub>   | _                                                 | I <sub>OL</sub> = 3mA            | 0                     |       | 0.4                    | V      |

| Input cap         | acitance                                          |                                  |                       | 5     |                        | pF     |

| POWER             | SUPPLY REQUIREMENTS                               | - ·                              |                       |       |                        |        |

| Power-            | AV <sub>DD</sub>                                  |                                  | 2.70                  | 3     | 3.3                    | V      |

| supply            | DV <sub>DD</sub>                                  |                                  | 2.70                  |       | 3.3                    | V      |

| voltage           | BV <sub>DD</sub> <sup>(6)</sup>                   |                                  | 2.70                  |       | 3.3                    | V      |

|                   |                                                   | In normal operation              |                       | 10    | 15                     | mA     |

| Quiescen          | at current of AV <sub>DD</sub>                    | All power-down                   |                       | 1     |                        | mA     |

| Quiescen          | t current of DV <sub>DD</sub>                     |                                  |                       | 0.3   |                        | mA     |

| Quiescen          | t current of BV <sub>DD</sub>                     |                                  |                       | 0.1   |                        | mA     |

| Power dis         | ssipation                                         |                                  |                       | 60    |                        | mW     |

| TEMPER            | ATURE RANGE                                       | 1                                | I                     |       |                        |        |

|                   | performance                                       |                                  | -40                   |       | +85                    | °C     |

| Storage           |                                                   |                                  | -65                   |       | +150                   | °C     |

Bit GREF in AMC Status/Configuration Register determines the internal reference voltage. GREF must be cleared when AV<sub>DD</sub> is less (5) than 5V and the internal reference is selected (see AMC Status/Configuration Register for details).  $BV_{DD}$  must be not greater than  $AV_{DD}$  or  $DV_{DD}$ .

(6)

TEXAS INSTRUMENTS

www.ti.com

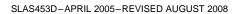

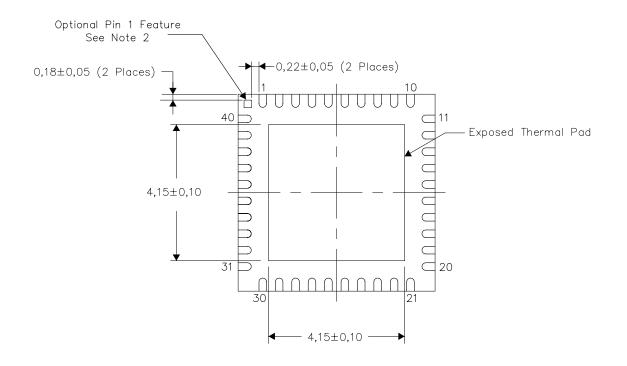

**PIN CONFIGURATION**

NOTE: (1) Thermal pad must be connected to the analog ground; refer to the package drawing for more information.

#### TERMINAL FUNCTIONS

|     | TERMINAL           | DESCRIPTION                                                                                                                                                                                                                                                                           |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME               | DESCRIPTION                                                                                                                                                                                                                                                                           |

| 1   | GALR               | Global analog input out-of-range alarm. GALR pin goes low (active) when one (or more) of the first four accessed analog inputs is out of preset range.                                                                                                                                |

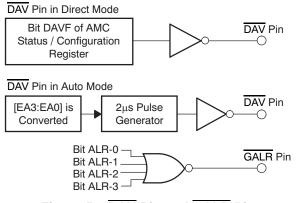

| 2   | DAV                | Data available indicator. In the direct mode, DAV pin goes low (active) when the conversion finishes.<br>In Auto-mode, a 2µs pulse (active low) appears on this pin when conversion cycle finishes (see ADC<br>Operation and Registers for details). DAV stays high when deactivated. |

| 3   | ELDAC              | External DAC synchronous load trigger. DACs that have external synchronous load selected are updated simultaneously by the rising edge of ELDAC.                                                                                                                                      |

| 4   | ISET_RESISTOR      | The resistor connected from analog supply to this pin sets the current output from the pin PRECISION_I_OUTPUT.                                                                                                                                                                        |

| 5   | PRECISION_I_OUTPUT | Current output to drive a thermistor.                                                                                                                                                                                                                                                 |

| 6   | DAC 0_OUT          | Output of DAC 0                                                                                                                                                                                                                                                                       |

| 7   | DAC 1_OUT          | Output of DAC 1                                                                                                                                                                                                                                                                       |

| 8   | DAC 2_OUT          | Output of DAC 2                                                                                                                                                                                                                                                                       |

| 9   | DAC 3_OUT          | Output of DAC 3                                                                                                                                                                                                                                                                       |

| 10  | SGND               | Analog input signal ground. This pin must connect to the ground of the analog input source in order to minimize digital noise.                                                                                                                                                        |

#### SLAS453D-APRIL 2005-REVISED AUGUST 2008

# **TERMINAL FUNCTIONS (continued)**

|     | TERMINAL    | DECODIDETION                                                                                                                                                                                                                          |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | DESCRIPTION                                                                                                                                                                                                                           |

| 11  | CH0         | Analog input channel 0                                                                                                                                                                                                                |

| 12  | CH1         | Analog input channel 1                                                                                                                                                                                                                |

| 13  | CH2         | Analog input channel 2                                                                                                                                                                                                                |

| 14  | CH3         | Analog input channel 3                                                                                                                                                                                                                |

| 15  | AGND        | Analog ground                                                                                                                                                                                                                         |

| 16  | AVDD        | Analog power supply, +3V to +5V. Must be the same value as DVDD.                                                                                                                                                                      |

| 17  | CH4         | Analog input channel 4                                                                                                                                                                                                                |

| 18  | CH5         | Analog input channel 5                                                                                                                                                                                                                |

| 19  | CH6         | Analog input channel 6                                                                                                                                                                                                                |

| 20  | CH7         | Analog input channel 7                                                                                                                                                                                                                |

| 21  | EXT_REF_IN  | When external reference connects here, the internal reference is overridden. When internal reference is selected, this pin works as output of the internal reference (with 10kΩ output impedance). See Reference section for details. |

| 22  | DAC 4_OUT   | Output of DAC 4                                                                                                                                                                                                                       |

| 23  | DAC 5_OUT   | Output of DAC 5                                                                                                                                                                                                                       |

| 24  | DAC 6_OUT   | Output of DAC 6                                                                                                                                                                                                                       |

| 25  | DAC 7_OUT   | Output of DAC 7                                                                                                                                                                                                                       |

| 26  | RESET       | Reset input. Logic low on this pin causes the part to perform hardware reset.                                                                                                                                                         |

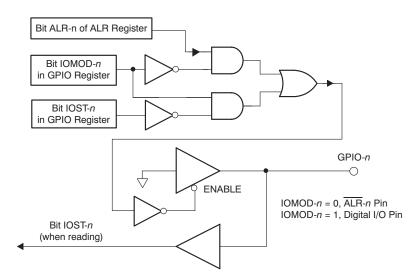

| 27  | GPIO-0/ALR0 | Multiple function I/O pin. Works as digital I/O or ALR pin of the first analog input.                                                                                                                                                 |

| 28  | GPIO-1/ALR1 | Multiple function I/O pin. Works as digital I/O or ALR pin of the second analog input.                                                                                                                                                |

| 29  | GPIO-2/ALR2 | Multiple function I/O pin. Works as digital I/O or ALR pin of the third analog input.                                                                                                                                                 |

| 30  | GPIO-3/ALR3 | Multiple function I/O pin. Works as digital I/O or ALR pin of the fourth analog input.                                                                                                                                                |

| 31  | CONVERT     | External conversion trigger. The rising edge starts sampling and conversion of the ADC when external trigger mode is selected.                                                                                                        |

| 32  | SCLK        | Serial clock input                                                                                                                                                                                                                    |

| 33  | MOSI        | Master out, slave in. Digital data input for the serial interface                                                                                                                                                                     |

| 34  | MISO        | Master in, slave out. Digital data output for the serial interface                                                                                                                                                                    |

| 35  | SS          | Slave select input (active low). Data is not clocked into MOSI unless $\overline{SS}$ is low. When $\overline{SS}$ is high, MISO is in high-impedance status.                                                                         |

| 36  | BVDD        | Interface power supply. Connects to 3V for 3V logic; connects to 5V for 5V logic.                                                                                                                                                     |

| 37  | DVDD        | Digital power supply (+3V to +5V). Must be the same value as AVDD.                                                                                                                                                                    |

| 38  | DGND        | Digital ground                                                                                                                                                                                                                        |

| 39  | GPIO-4      | General-purpose digital I/O pin                                                                                                                                                                                                       |

| 40  | GPIO-5      | General-purpose digital I/O pin                                                                                                                                                                                                       |

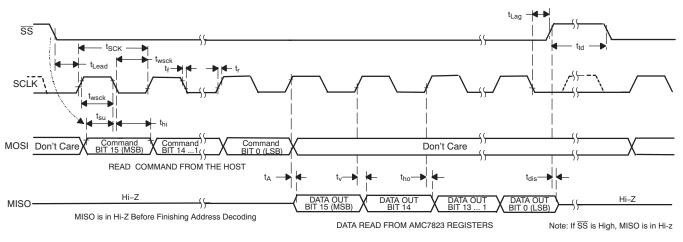

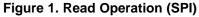

### **TIMING CHARACTERISTICS: +5V**

At –40°C to +85°C, AV<sub>DD</sub> = DV<sub>DD</sub> = 5V, and BV<sub>DD</sub> = 5V, unless otherwise noted.

|                      | PARAMETER                 | MIN MAX | UNIT |

|----------------------|---------------------------|---------|------|

| t <sub>sck</sub>     | SCLK period               | 42      | ns   |

| t <sub>wsck</sub>    | SCLK high or low time     | 21      | ns   |

| t <sub>Lead</sub>    | SS enable lead time       | 21      | ns   |

| t <sub>Lag</sub>     | SS enable lag time        | 21      | ns   |

| t <sub>td</sub>      | Sequential transfer delay | 42      | ns   |

| t <sub>su</sub>      | Data setup time           | 0       | ns   |

| t <sub>hi</sub>      | Data hold time (inputs)   | 21      | ns   |

| t <sub>ho</sub>      | Data hold time (outputs)  | 0       | ns   |

| t <sub>A</sub>       | Slave access time         | 21      | ns   |

| t <sub>dis</sub>     | Slave MISO disable time   | 21      | ns   |

| t <sub>v</sub>       | Data valid                | 10      | ns   |

| t <sub>r</sub>       | Rise time                 | 30      | ns   |

| t <sub>f</sub>       | Fall time                 | 30      | ns   |

| t <sub>WLDAC</sub>   | ELDAC width               | 210     | ns   |

| t <sub>CONVERT</sub> | CONVERT width             | 210     | ns   |

## TIMING CHARACTERISTICS: +3V

At –40°C to +85°C,  $AV_{DD} = DV_{DD} = 3V$ , and  $BV_{DD} = 3V$ , unless otherwise noted.<sup>(1)</sup>

|                      | PARAMETER                 | MIN | MAX | UNIT |

|----------------------|---------------------------|-----|-----|------|

| t <sub>sck</sub>     | SCLK period               | 84  |     | ns   |

| t <sub>wsck</sub>    | SCLK high or low time     | 42  |     | ns   |

| t <sub>Lead</sub>    | SS enable lead time       | 42  |     | ns   |

| t <sub>Lag</sub>     | SS enable lag time        | 42  |     | ns   |

| t <sub>td</sub>      | Sequential transfer delay | 84  |     | ns   |

| t <sub>su</sub>      | Data setup time           | 0   |     | ns   |

| t <sub>hi</sub>      | Data hold time (inputs)   | 42  |     | ns   |

| t <sub>ho</sub>      | Data hold time (outputs)  | 0   |     | ns   |

| t <sub>A</sub>       | Slave access time         |     | 42  | ns   |

| t <sub>dis</sub>     | Slave MISO disable time   |     | 42  | ns   |

| t <sub>v</sub>       | Data valid                |     | 10  | ns   |

| t <sub>r</sub>       | Rise time                 |     | 30  | ns   |

| t <sub>f</sub>       | Fall time                 |     | 30  | ns   |

| t <sub>WLDAC</sub>   | ELDAC width               | 420 |     | ns   |

| t <sub>CONVERT</sub> | CONVERT width             | 420 |     | ns   |

(1) For  $AV_{DD} = DV_{DD} = 5V$ ,  $BV_{DD} = 3V$ , refer to the specification shown in this table.

Figure 2. Write Operation (SPI)

Texas

www.ti.com

INSTRUMENTS

100

www.ti.com

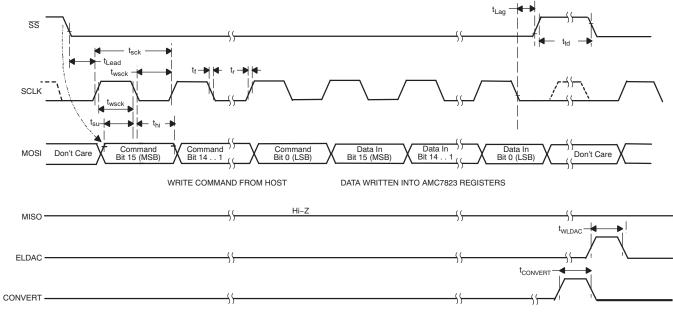

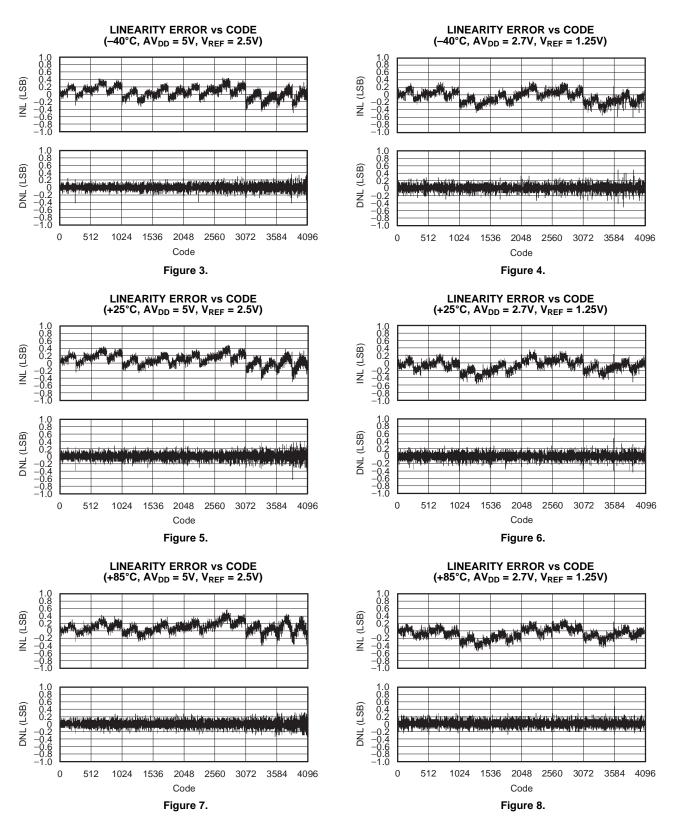

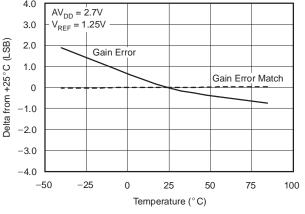

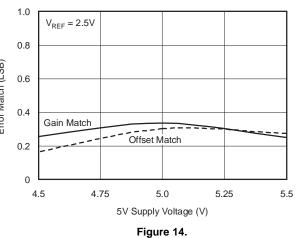

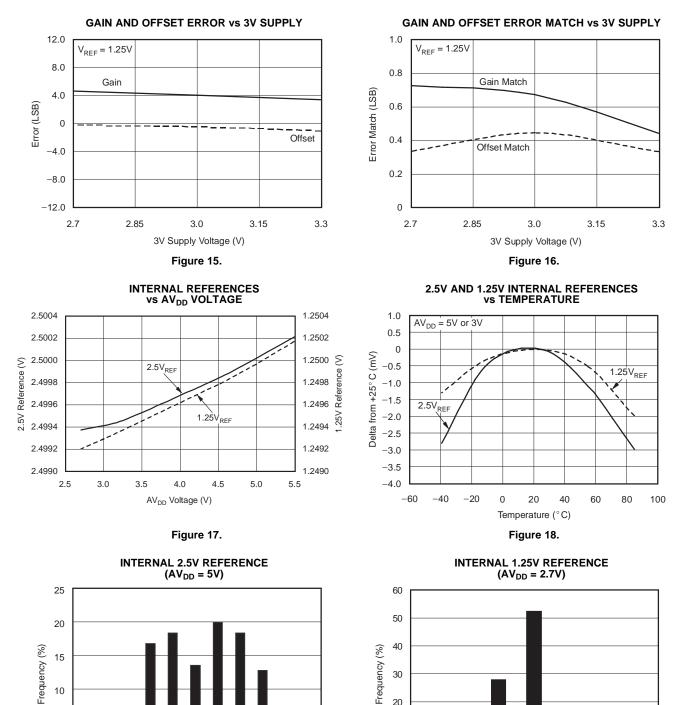

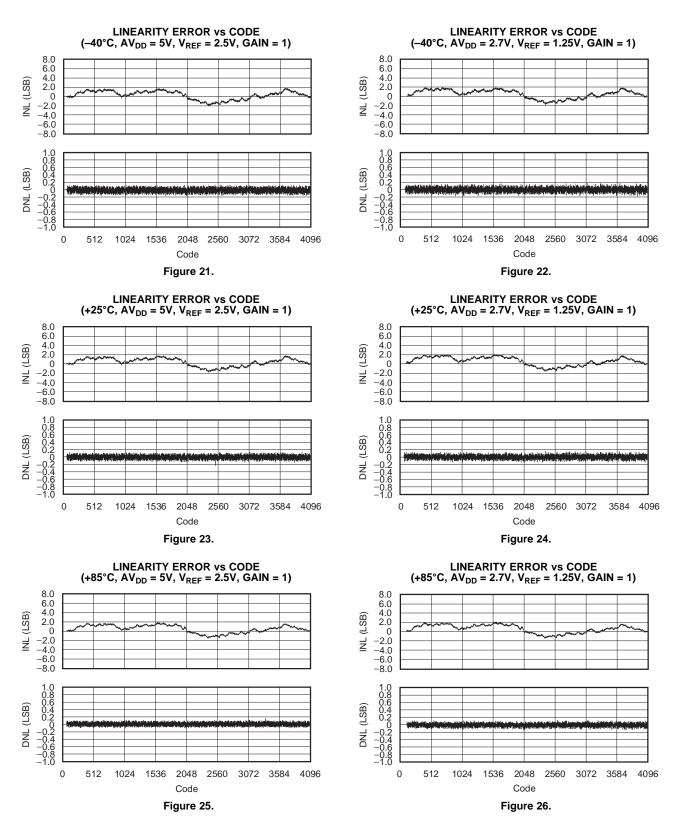

# TYPICAL CHARACTERISTICS: ANALOG-TO-DIGITAL CONVERTER (ADC) (continued)

At +25°C,  $AV_{DD} = DV_{DD} = 5V$ , unless otherwise noted.

Copyright © 2005–2008, Texas Instruments Incorporated

# TYPICAL CHARACTERISTICS: ANALOG-TO-DIGITAL CONVERTER (ADC) (continued)

At +25°C,  $AV_{DD} = DV_{DD} = 5V$ , unless otherwise noted.

14 Submit Documentation Feedback

2.497

2.499

2.500

Histogram Bins (V) Figure 19.

2.501

2.502 2.503

2.498

10

5

0

2.495 2.496 2.505

2.504

20

10

0

1.247

1.248

Copyright © 2005–2008, Texas Instruments Incorporated

1.251

1.252

1.253

1.250

Histogram Bins (V)

Figure 20.

1.249

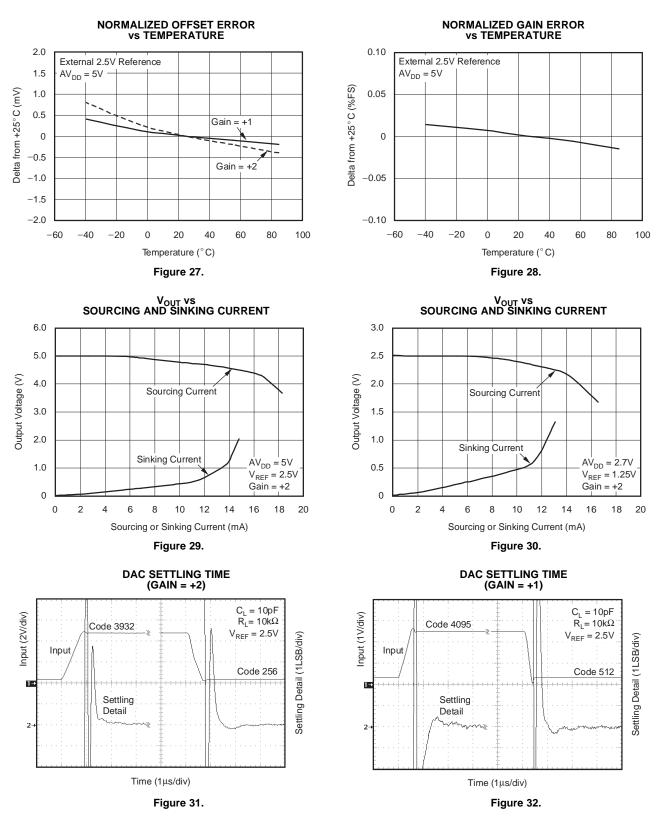

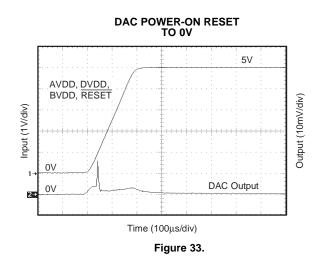

# TYPICAL CHARACTERISTICS: DIGITAL-TO-ANALOG CONVERTER (DAC)

# TYPICAL CHARACTERISTICS: DIGITAL-TO-ANALOG CONVERTER (DAC) (continued)

# TYPICAL CHARACTERISTICS: DIGITAL-TO-ANALOG CONVERTER (DAC) (continued)

At +25°C,  $AV_{DD} = DV_{DD} = 5V$ , unless otherwise noted.

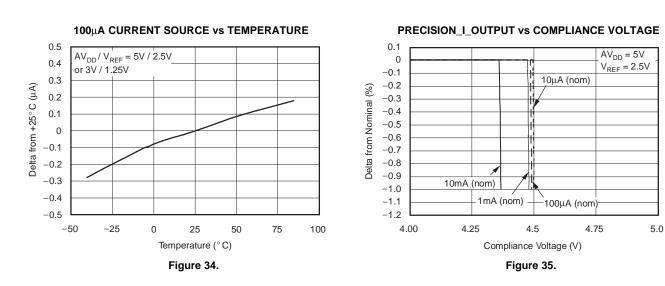

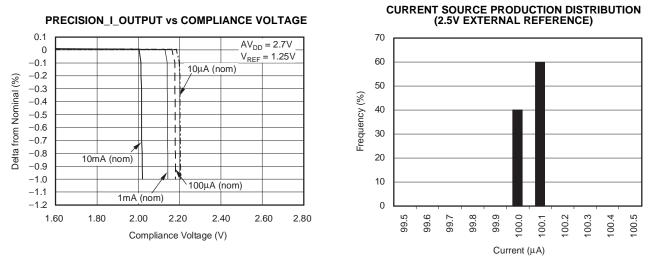

# **TYPICAL CHARACTERISTICS: PRECISION CURRENT SOURCE**

# TYPICAL CHARACTERISTICS: PRECISION CURRENT SOURCE (continued)

At +25°C,  $AV_{DD} = DV_{DD} = 5V$ , unless otherwise noted.

Figure 36.

Figure 37.

CURRENT SOURCE PRODUCTION DISTRIBUTION (1.25V EXTERNAL REFERENCE)

TEXAS INSTRUMENTS

www.ti.com

# **APPLICATION INFORMATION**

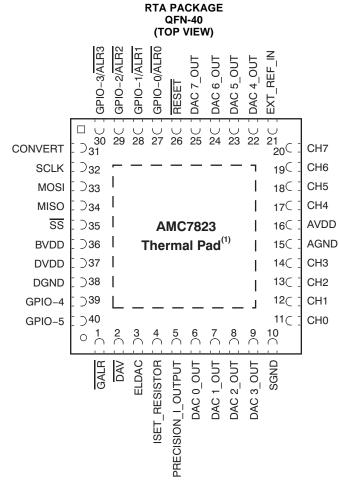

## DIGITAL INTERFACE

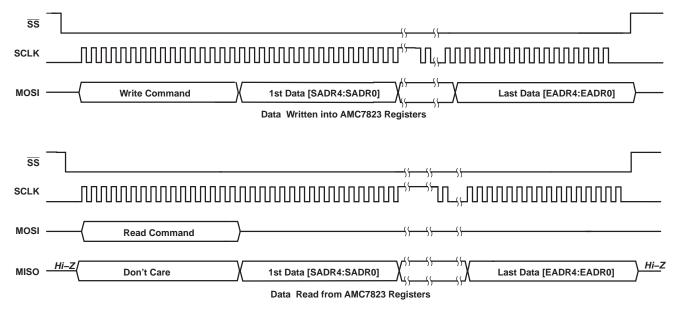

The AMC7823 communicates through a standard SPI bus. The SPI allows full-duplex, synchronous, serial communication between a host processor (the master) and peripheral devices (slaves). The SPI master generates the synchronizing clock and initiates transmissions. SPI slave devices, such as the AMC7823, depend on a master to start and synchronize transmissions.

A transmission begins when initiated by an SPI master. A word from the master is shifted into the AMC7823 through the MOSI pin under the control of the master serial clock, SCLK. A word from an AMC7823 register is shifted out from the MISO pin under the control of SCLK as well.

The idle state of the serial clock for the AMC7823 is low, which corresponds to a clock polarity setting of 0 (typical microprocessor SPI control bit CPOL = '0'). The AMC7823 interface is designed with a clock phase setting of 1 (typical microprocessor SPI control bit CPHA = '1'). In both the master and the slave, data are shifted out on the rising edge of SCLK and sampled on the falling edge of SCLK where data are stable. The master begins driving the MOSI pin on the first rising edge of SCLK after SS is activated (low).

To write data into AMC7823, the host activates the slave select signal ( $\overline{SS}$  = low) and issues a WRITE command to start the data transmission. The AMC7823 always interprets the first word (from the host) immediately following the falling edge of  $\overline{SS}$  signal as a command. The data to be written into the AMC7823 follow the command. The slave select pin ( $\overline{SS}$ ) must remain low until all data are transmitted (see Figure 39). Otherwise, the WRITE operation is terminated. Likewise, to read data from AMC7823, the host activates the slave select signal and sends a READ command. The AMC7823 then sends data out through the MISO pin under the control of SCLK. The slave select pin must remain low until all data are shifted out (see Figure 39). Otherwise, the transmission is terminated, and all remaining data (if any) are ignored.

When the operation is terminated, the master must issue a new command to start a new operation.

All registers in the AMC7823 are 16-bit. It takes 16 clock pulses of SCLK to transfer one data or command word. <u>All</u> data are transferred into (or out of) the AMC7823 through an internal serial-parallel (parallel-serial) register. If <u>SS</u> is deactivated (that is, goes high) before the 16th clock finishes, the incomplete transfer is terminated immediately and the data being transferred are ignored. In a write operation, the data are not written into the AMC7823 register. In a read operation, the remaining data bits are not shifted out, and the data must be ignored.

### **AMC7823 COMMUNICATION PROTOCOL**

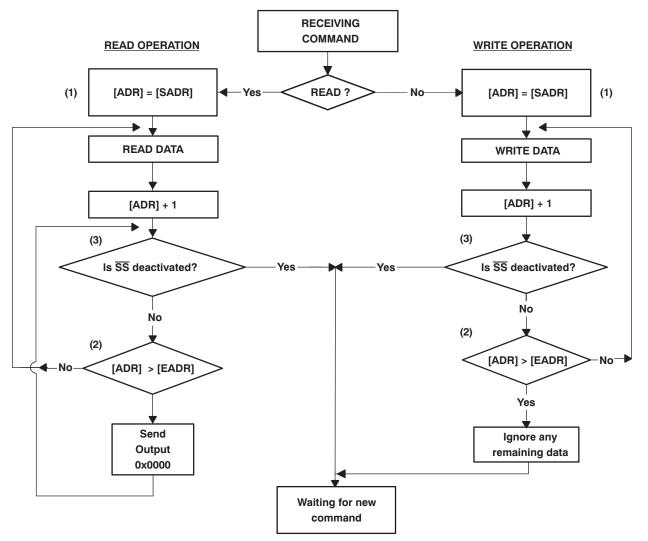

With the exception of two external trigger pins, an external RESET pin, and an external current setting resistor, the AMC7823 is entirely controlled by registers. Reading from and writing to these registers is accomplished by issuing a 16-bit command word followed immediately by data for a single register or for a range of registers. This command word is constructed as shown in the Command Format table. The data word(s) format for the target register(s) are illustrated in subsequent pages of this document.

#### Command Format

| Bit 15<br>MSB | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>LSB |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| R/W           | х      | PG1    | PG0    | х      | SADR4  | SADR3 | SADR2 | SADR1 | SADR0 | Х     | EADR4 | EADR3 | EADR2 | EADR1 | EADR0        |

X : Don't Care

Where:

$R/\overline{W}$ : Data flow direction bit.

$R/\overline{W}$  = '1'. Read operation. Data are transferred from AMC7823 to the host.

R/W = '0'. Write operation. Data are transferred from the host to AMC7823.

PG1 – PG0: Memory page of addressed register(s) (see Table 1).

SADR4 – SADR0: Starting address of register(s) on selected page.

EADR4 – EADR0: Ending address of register(s) on selected page.

**NOTE:** If the ending address is equal to or smaller than the starting address, only the starting address is accessed. In this case, the operation applies only to the starting address; all remaining data and memory locations (if any) are ignored. In this manner, a single register may be addressed by setting [EADR4:EADR0] = 00000 or [SADR4:SADR0]  $\geq$  [EADR4:EADR0].

| PG1 | PG0 | PAGE ADDRESS |

|-----|-----|--------------|

| 0   | 0   | 0            |

| 0   | 1   | 1            |

| 1   | 0   | Reserved     |

| 1   | 1   | Reserved     |

| 1   | 1   | Reserved     |

#### Table 1. Page Addressing

For example, to read the register with address 0x00 on page 0, the host processor must send the AMC7823 the command 0x8000; this command specifies a read operation on page 0, address 0. After sending the command, the host reads one data word. To read the registers 0x02 to 0x07 on page 0 (ADC Data-2 to ADC Data-7), the host must send 0x8087 first, and then clock six data words sequentially out of the AMC7823. The first data word is from 0x02, the second from 0x03, and the sixth from 0x07. If the host continues clocking data out after reading the last location [EADR4:EADR0], the value 0x0000 is output until the operation stops. However, if the host deactivates SS before reading the last register, the operation is terminated and all remaining registers are ignored.

Likewise, to load data into the registers with addresses 0x03 to 0x05 on page 1 (DAC-3 Data Register to DAC-5 Data Register), the host sends command 0x10C5 followed sequentially by three data words. The first word is written into 0x03 of page 1, the second goes to 0x04, and the third goes to 0x05. If the host continues to transfer data into AMC7823 after writing the last location [EADR4:EADR0], all these data are ignored until the operation stops. However, if the host deactivates SS before writing the last location, the operation is terminated and all remaining locations are ignored.

See the AMC7823 Memory Map (Table 2) for details of register locations.

Figure 39 shows an example of a complete data transaction between the host processor and the AMC7823.

Figure 39. Write and Read Operations of the AMC7823 Interface

## AMC7823 MEMORY MAP

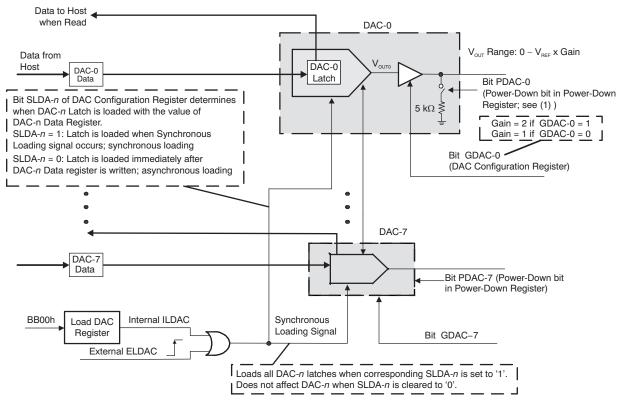

The AMC7823 has several 16-bit registers separated into two pages of memory, Page 0 and Page 1. The memory map is shown in Table 2. Locations that are marked **Reserved** read back 0x0000 if they are read by the host. Writing to these locations has no effect. Figure 40 explains the Read/Write operation.

| Page 0: Data/Status Registers |     |         |               | Page 1: Control/Setting Registers |     |               |                          |

|-------------------------------|-----|---------|---------------|-----------------------------------|-----|---------------|--------------------------|

| Address                       | R/W | Default | Register Name | Address R/W Default Register      |     | Register Name |                          |

| 00                            | R   | 0x0000  | ADC-0 Data    | 00                                | R/W | 0x0000        | DAC-0 Data               |

| 01                            | R   | 0x0000  | ADC-1 Data    | 01                                | R/W | 0x0000        | DAC-1 Data               |

| 02                            | R   | 0x0000  | ADC-2 Data    | 02                                | R/W | 0x0000        | DAC-2 Data               |

| 03                            | R   | 0x0000  | ADC-3 Data    | 03                                | R/W | 0x0000        | DAC-3 Data               |

| 04                            | R   | 0x0000  | ADC-4 Data    | 04                                | R/W | 0x0000        | DAC-4 Data               |

| 05                            | R   | 0x0000  | ADC-5 Data    | 05                                | R/W | 0x0000        | DAC-5 Data               |

| 06                            | R   | 0x0000  | ADC-6 Data    | 06                                | R/W | 0x0000        | DAC-6 Data               |

| 07                            | R   | 0x0000  | ADC-7 Data    | 07                                | R/W | 0x0000        | DAC-7 Data               |

| 08                            | R   | 0x0000  | ADC-8 Data    | 08                                | R/W | 0x0000        | LOAD DAC                 |

| 09                            | R   | 0x0000  | ALR Register  | 09                                | R/W | 0x0000        | DAC Configuration        |

| 0A                            | R/W | 0xFFFF  | GPIO Register | 0A                                | R/W | 0x4000        | AMC Status/Configuration |

| 0B                            |     |         | Reserved      | 0B                                | R/W | 0x0000        | ADC Control              |

| 0C                            |     |         | Reserved      | 0C                                | R/W | 0x0000        | RESET                    |

| 0D                            |     |         | Reserved      | 0D                                | R/W | 0x0000        | Power-Down               |

| 0E                            |     |         | Reserved      | 0E                                | R/W | 0x0FFF        | Threshold-Hi-0           |

| 0F                            |     |         | Reserved      | 0F                                | R/W | 0x0000        | Threshold-Low-0          |

| 10                            |     |         | Reserved      | 10                                | R/W | 0x0FFF        | Threshold-Hi-1           |

| 11                            |     |         | Reserved      | 11                                | R/W | 0x0000        | Threshold-Low-1          |

| 12                            |     |         | Reserved      | 12                                | R/W | 0x0FFF        | Threshold-Hi-2           |

| 13                            |     |         | Reserved      | 13                                | R/W | 0x0000        | Threshold-Low-2          |

| 14                            |     |         | Reserved      | 14                                | R/W | 0x0FFF        | Threshold-Hi-3           |

| 15                            |     |         | Reserved      | 15                                | R/W | 0x0000        | Threshold-Low-3          |

| 16                            |     |         | Reserved      | 16                                |     |               | Reserved                 |

| 17                            |     |         | Reserved      | 17                                |     |               | Reserved                 |

| 18                            |     |         | Reserved      | 18                                |     |               | Reserved                 |

| 19                            |     |         | Reserved      | 19                                |     |               | Reserved                 |

| 1A                            |     |         | Reserved      | 1A                                |     |               | Reserved                 |

| 1B                            |     |         | Reserved      | 1B                                |     |               | Reserved                 |

| 1C                            |     |         | Reserved      | 1C                                |     |               | Reserved                 |

| 1D                            |     |         | Reserved      | 1D                                |     |               | Reserved                 |

| 1E                            |     |         | Reserved      | 1E                                | R   | 0xE000        | Part Revision Number     |

| 1F                            |     |         | Reserved      | 1F                                |     |               | Reserved                 |

#### Table 2. AMC7823 Memory Map

INSTRUMENTS

**EXAS**

- (1) [SADR] represents the start address, which is specified by bits [PG1:PG0] and [SADR4:SADR0] in the command word. [ADR] represents the current address.

- (2) [EADR] represents the end address, which is specified by bits [PG0:PG1] and [EADR4:EADR0] in the command word.

- (3) Host ends data transfer by deactivating  $\overline{SS}$ .

### Figure 40. Read/Write Operations

Texas Instruments

www.ti.com

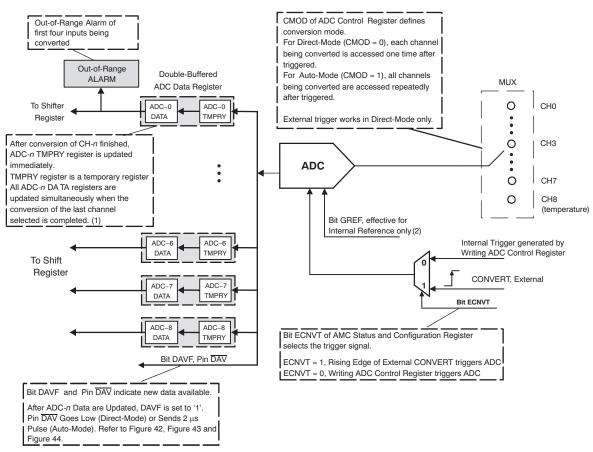

# ADC OPERATION (See AMC Status/Configuration Register and ADC Control Register)

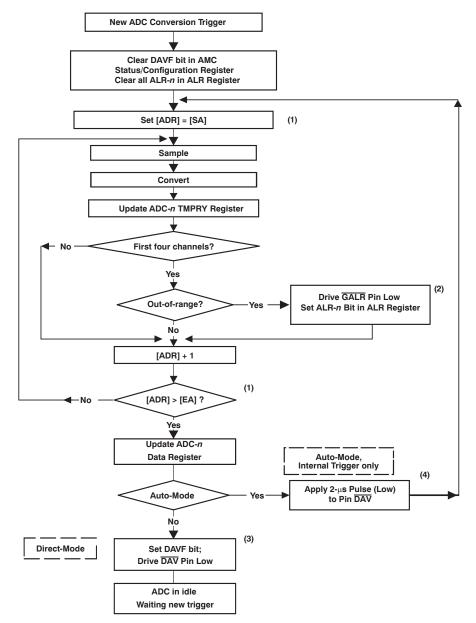

- (1) To avoid conflict, the data are not loaded into ADC-*n* data register from ADC-*n* temporary register until the data transfer from the ADC-*n* data register to the shift register (if any) finishes.

- (2) When the internal reference is selected, the bit GREF determines the input range: GREF = '0', 0 to 2.5V; GREF = '1', 0 to 5V (for 5V supply only). When an external reference is selected, the input range is 0 to 2 ×  $V_{REF}$ . The input cannot be above AV<sub>DD</sub>.

#### Figure 41. ADC Structure

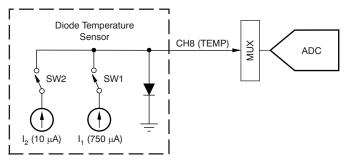

The ADC has nine analog inputs. Channels CH0 through CH7 receive external analog inputs. CH8 is dedicated to the on-chip temperature sensor (see On-chip Temperature Sensor section).

### ADC Trigger Signals (see AMC Status/Configuration Register)

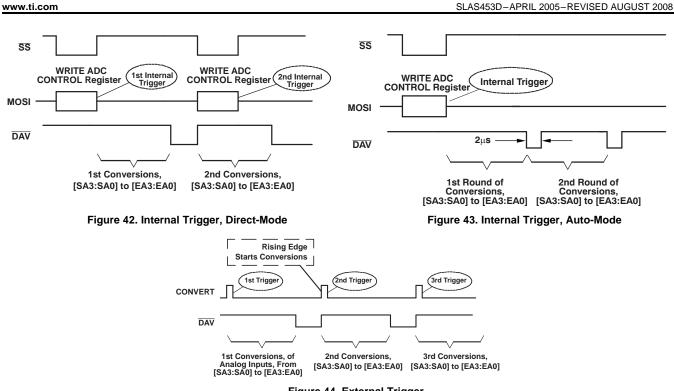

The ADC can be triggered externally (external trigger mode) or internally (internal trigger mode). Bit ECNVT (Enable CONVERT) of the AMC Status/Configuration Register determines which mode is used. When ECNVT is set to '1', the ADC works in external trigger mode and the rising edge of the external signal CONVERT initiates data conversion. When ECNVT is cleared to '0', the ADC is in internal trigger mode, and writing to the ADC Control Register initiates conversion.

After the ADC is triggered, a group of analog inputs (up to nine channels may be specified) are multiplexed and each channel is converted. The starting and ending addresses of the group of channels are specified by the bits [SA3:SA0] and [EA3:EA0], respectively, in the ADC Control Register (see ADC Control Register for details). The specified channels are converted sequentially from the starting to the ending address according to Table 12 (Analog Input Channel Address Map) and Table 13 (Analog Input Channel Range).

#### Conversion Mode

When internal trigger mode is selected (ECNVT = '0'), two types of ADC conversion are available: direct-mode and auto-mode. The bit CMODE (Conversion MODE) of the ADC Control Register specifies the conversion mode. When external trigger mode is selected (ECNVT = '1'), only direct-mode conversion is available. In this case, bit CMODE in the ADC Control Register is ignored. (See Table 3.)

In direct-mode, each analog channel within the specified group is converted a single time. After the last channel is converted, the ADC goes into idle state and waits for a new trigger.

Auto-mode is a continuous operation. In auto-mode, each analog channel within the specified group is converted sequentially from [SA3:SA0] to [EA3:EA0] and repeatedly until one of the following events occur:

- a new internal trigger is issued;

- the conversion mode is changed to direct-mode by rewriting the ADC Control Register; or

- the external trigger is enabled by rewriting the AMC Status/Configuration Register.

When a new internal trigger is issued, a new conversion process starts.

Table 3 summarizes the ADC conversion modes. Note that the ending address must not be less than the starting address. Otherwise, the ADC conversion sequence may not be correct.

| Table 3. ADC C | onversion Modes |

|----------------|-----------------|

|----------------|-----------------|

| ECNVT OF AMC STATUS/<br>CONFIGURATION REGISTER | CMODE OF<br>ADC CONTROL REGISTER | ADC CONVERSION MODE           |

|------------------------------------------------|----------------------------------|-------------------------------|

| 1                                              | -                                | External Trigger, Direct-Mode |

| 0                                              | 0                                | Internal Trigger, Direct-Mode |

| 0                                              | 1                                | Internal Trigger Auto-Mode    |

#### **Double-Buffered ADC Data Register**

The host can access all nine double-buffered ADC Data registers. The conversion result from the analog input with the channel address n is stored in the ADC-n Data register. When the conversion of an individual channel is completed, the data is immediately transferred into the corresponding ADC-n temporary (TMPRY) register, the first stage of the data buffer. When the conversion of the last channel ([EA3:EA0]) finishes, all data in ADC-n TMPRY registers are transferred simultaneously into the corresponding ADC-n Data registers, the second stage of the data buffer. However, if a data transfer is in progress between an ADC-n Data Register and the AMC Shift Register, this ADC-n Data Register is not updated until the data transfer is complete. The conversion result from channel address n is stored in the ADC-n Data Register. For example, the result from channel [0x04] is stored in the ADC-4 Data Register, and the result from channel [0x07] is stored in the ADC-7 Data Register. The ADC-8 Data Register is used to store on-chip temperature measurement data (see the On-chip Temperature Sensor).

#### SCLK Clock Noise

The host activates the slave select signal  $\overline{SS}$  (low) to access the AMC7823. When  $\overline{SS}$  is high, the SCLK clock is blocked. To avoid noise caused by SCLK clock, deactivate  $\overline{SS}$  (high) for at least the conversion process time immediately after the ADC conversion starts.

### Handshaking with the Host (see AMC Status/Configuration Register)

The  $\overline{\text{DAV}}$  pin and the bit DAVF (Data Available Flag) of the AMC Status/Configuration Register provide handshaking with the host. Pin and bit status depend on the conversion mode (direct or auto). In direct-mode, after ADC-*n* Data registers of all of the selected channels are updated, the DAVF bit in the AMC Status/Configuration Register is set immediately to '1', and the DAV pin is active (low) to signify new data are available. Reading the ADC-*n* Data Register or restarting the ADC clears bit DAVF to '0' and deactivates the DAV pin (high).